2

3

4

5

**Document Identifier: DSP0282**

Date: 2024-10-09

Version: 1.0.1

- Memory-Mapped Buffer Interface (MMBI)

- 7 Specification

8 Supersedes: 1.0.0

9 **Document Class: Normative**

10 Document Status: Published

11 Document Language: en-US

- 12 Copyright Notice

- 13 Copyright © 2023–2024 DMTF. All rights reserved.

- 14 DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems

- 15 management and interoperability. Members and non-members may reproduce DMTF specifications and

- 16 documents for uses consistent with this purpose, provided that correct attribution is given. As DMTF

- 17 specifications may be revised from time to time, the particular version and release date should always be

- 18 noted.

- 19 Implementation of certain elements of this standard or proposed standard may be subject to third-party

- 20 patent rights, including provisional patent rights (herein "patent rights"). DMTF makes no representations

- 21 to users of the standard as to the existence of such rights and is not responsible to recognize, disclose, or

- 22 identify any or all such third-party patent right owners or claimants, nor for any incomplete or inaccurate

- 23 identification or disclosure of such rights, owners, or claimants. DMTF shall have no liability to any party,

- 24 in any manner or circumstance, under any legal theory whatsoever, for failure to recognize, disclose, or

- 25 identify any such third-party patent rights, or for such party's reliance on the standard or incorporation

- thereof in its products, protocols, or testing procedures. DMTF shall have no liability to any party

- 27 implementing such standards, whether such implementation is foreseeable or not, nor to any patent

- 28 owner or claimant, and shall have no liability or responsibility for costs or losses incurred if a standard is

- 29 withdrawn or modified after publication, and shall be indemnified and held harmless by any party

- 30 implementing the standard from any and all claims of infringement by a patent owner for such

- 31 implementations.

- 32 For information about patents held by third parties which have notified DMTF that, in their opinion, such

- 33 patents may relate to or impact implementations of DMTF standards, visit

- 34 https://www.dmtf.org/about/policies/disclosures.

- 35 All other marks and brands are the property of their respective owners.

- 36 This document's normative language is English. Translation into other languages is permitted.

37 CONTENTS

| 38       | For  | eword   | j                                                              | 6  |

|----------|------|---------|----------------------------------------------------------------|----|

| 39       | Intr | oductio | ion                                                            | 7  |

| 40       | 1    | Scop    | pe                                                             | 8  |

| 41       | 2    | Norm    | mative references                                              | 8  |

| 42       | 3    | Term    | ns and definitions                                             | 8  |

| 43       | 4    | Conv    | ventions                                                       | 10 |

| 44       | -    | 4.1     | Reserved and unassigned values                                 |    |

| 45       |      | 4.2     | Byte ordering                                                  |    |

| 46       | 5    | Assu    | umptions                                                       | 10 |

| 47       |      | 5.1     | Underlying Memory Mapping                                      |    |

| 48       |      | 5.2     | Multiple Instances                                             | 10 |

| 49       |      | 5.3     | Resets and Errors                                              |    |

| 50       |      | 5.4     | Notifications (Interrupts)                                     |    |

| 51       |      | 5.5     | Packet Sizes, Types, and Packet Flow                           |    |

| 52       |      | 5.6     | Security                                                       |    |

| 53       | 6    |         | ic Architecture Concept                                        |    |

| 54       | 7    |         | BI Data Structures                                             |    |

| 55       |      | 7.1     | MMBI Capability Descriptor                                     |    |

| 56       |      | 7.2     | MMBI Circular Buffers—Variable Packet Size Circular Buffer     |    |

| 57       |      |         | 7.2.1 Variable Packet Size Circular Buffer Descriptor          |    |

| 58<br>59 |      |         | 7.2.2 Host Read-Write Structure                                |    |

|          | 0    | Dunt    | · · · · · · · · · · · · · · · · · · ·                          |    |

| 60<br>61 | 8    | 8.1     | time Flows                                                     |    |

| 62       |      | 0.1     | 8.1.1 Initialization of Descriptor Structures after Power Up   |    |

| 63       |      |         | 8.1.2 Interface States and Graceful Reset                      |    |

| 64       |      |         | 8.1.3 Ungraceful Reset Considerations                          |    |

| 65       |      | 8.2     | Calculation of Filled Space and Empty Space in Circular Buffer |    |

| 66       |      | 8.3     | Device Readiness and Communication Pause                       |    |

| 67       |      | 8.4     | Packet Transfer                                                | 31 |

| 68       |      | 8.5     | Interrupts (Optional)                                          | 32 |

| 69       | 9    | Multi   | ti-Protocol Packet Format                                      | 32 |

| 70       | AN   | NEX A   | A (informative) Notations                                      | 34 |

| 71       |      |         | 3 (informative) Change log                                     |    |

| 72       |      |         | · , , , , , , , , , , , , , , , , , , ,                        |    |

# 73 **Figures**

| 74 | Figure 1 – Multiple MMBI Instances                    | 11 |

|----|-------------------------------------------------------|----|

| 75 | Figure 2 – MMBI Interface Concept Overview            | 13 |

| 76 | Figure 3 – MMBI Data Structure Relationships          | 14 |

| 77 | Figure 4 – MMBI Capability Descriptor Layout          | 15 |

| 78 | Figure 5 – MMBI Interface States                      | 25 |

| 79 | Figure 6 – Sample MMBI Reset by Host                  | 26 |

| 80 | Figure 7 – Sample MMBI Reset by (B)MC                 | 28 |

| 81 | Figure 8 – Filled and Empty Space in Circular Buffers | 29 |

| 82 | Figure 9 – Sample MMBI Device Pause Sequences         | 30 |

| 83 |                                                       |    |

|    |                                                       |    |

# Tables

84

| 85 | Table 1 – MMBI Capability Descriptor Structure (MMBI_Desc)                   | 15 |

|----|------------------------------------------------------------------------------|----|

| 86 | Table 2 – Buffer Type Dependent Descriptor for BUFT=0001b (VPSCB Descriptor) | 17 |

| 87 | Table 3 – MMBI Host Read-Write Structure (Host_RWS)                          | 19 |

| 88 | Table 4 – MMBI Host Read-Only Structure (Host_ROS)                           | 20 |

| 89 | Table 5 – MMBI Interface States                                              | 23 |

| 90 | Table 6 – Multi-Protocol Packet Format                                       | 33 |

| 91 |                                                                              |    |

| 92                                                                        | Foreword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 93<br>94                                                                  | The Memory-Mapped Buffer Interface (MMBI) Specification (DSP0282) was prepared by DMTF's PMCI Working Group.                                                                                                                                                                                                                                                                                                                                                                            |

| 95<br>96                                                                  | DMTF is a not-for-profit association of industry members dedicated to promoting enterprise and systems management and interoperability. For information about DMTF, visit <a href="mailto:dmtf.org">dmtf.org</a> .                                                                                                                                                                                                                                                                      |

| 97                                                                        | This version supersedes version 1.0.0. For a list of changes, see the change log in ANNEX B.                                                                                                                                                                                                                                                                                                                                                                                            |

| 98                                                                        | Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 99                                                                        | DMTF acknowledges the following individuals for their contributions to this document:                                                                                                                                                                                                                                                                                                                                                                                                   |

| 100                                                                       | Editors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 101<br>102                                                                | <ul> <li>Janusz Jurski – Intel Corporation</li> <li>Richard Marian Thomaiyar – Intel Corporation</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |

| 103                                                                       | DMTF Contributors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 104<br>105<br>106<br>107<br>108<br>109<br>110<br>111<br>112<br>113<br>114 | <ul> <li>Rama Bisa – Dell Inc.</li> <li>Patrick Caporale – Lenovo</li> <li>Samer El-Haj-Mahmoud – ARM Inc.</li> <li>Ted Emerson – Hewlett Packard Enterprise</li> <li>John Guan – Inspur</li> <li>Ramesha He – Dell Inc.</li> <li>Tiffany Kasanicky – Intel Corporation</li> <li>Mahesh Natu – Intel Corporation</li> <li>Chandra Nelogal – Dell Inc.</li> <li>Edward Newman – Hewlett Packard Enterprise</li> <li>Scott Phuong – Cisco</li> <li>Derek Roberts – Xilinx Inc.</li> </ul> |

| 116<br>117<br>118                                                         | William Scherer III – Hewlett Packard Enterprise Hemal Shah – Broadcom Inc.  Bob Stevens – Dell Inc.                                                                                                                                                                                                                                                                                                                                                                                    |

# 119 Introduction

| 400 | The Manual Manual Poffee Late for a MMDD Occasional lateral before the contraction of a Titalian    |

|-----|-----------------------------------------------------------------------------------------------------|

| 120 | The Memory-Mapped Buffer Interface (MMBI) Specification defines the mechanisms facilitating         |

| 121 | communication between platform components, typically host software and a Management Controller      |

| 122 | (usually a Baseboard Management Controller). Using the shared memory concept, this document defines |

| 123 | the MMBI protocol that allows packet exchanges between communicating devices. The described         |

| 124 | memory mapping makes it possible for both boot code (such as UEFI firmware), as well as OS-level    |

| 125 | software (such as OS kernel or drivers) to establish efficient communication with a (Baseboard)     |

| 126 | Management Controller at bandwidth and latency limited by the underlying memory mapping             |

| 127 | mechanisms. MMBI can also be used to enable communication between other types of platform           |

| 128 | components, not just host software and a Management Controller (MC) or a Baseboard Management       |

| 129 | Controller (BMC).                                                                                   |

## 130 **1 Scope**

- 131 This document provides the specifications for the Memory-Mapped Buffer Interface (MMBI). MMBI

- assumes an underlying memory mapping capability, such as PCIe MMIO/BAR, allowing host software to

- 133 efficiently access data stored in (B)MC memory. MMBI defines generic packet-based communication

- mechanism (based on circular buffers), and specific protocols, such as MCTP, should be covered in other

- 135 documents.

## 136 2 Normative references

- 137 The following referenced documents are indispensable for the application of this document. For dated or

- versioned references, only the edition cited (including any corrigenda or DMTF update versions) applies.

- For references without a date or version, the latest published edition of the referenced document

- 140 (including any corrigenda or DMTF update versions) applies.

- 141 DMTF, DSP0236, Management Component Transport Protocol (MCTP) Base Specification 1.3,

- 142 https://www.dmtf.org/standards/published\_documents/DSP0236\_1.3.pdf

- 143 DMTF, DSP0239, Management Component Transport Protocol (MCTP) IDs and Codes 1.10,

- https://www.dmtf.org/standards/published\_documents/DSP0239\_1.10.pdf

- DMTF, DSP0276, Secured Messages using SPDM over MCTP Binding Specification 1.1.0,

- https://www.dmtf.org/standards/published\_documents/DSP0276\_1.1.0.pdf

- 147 DMTF, DSP0284, Management Component Transport Protocol (MCTP) Memory-Mapped Buffer Interface

- 148 (MMBI) Transport Binding Specification 1.0,

- 149 https://www.dmtf.org/standards/published documents/DSP0284 1.0.pdf

- 150 IANA, Internet Assigned Numbers Authority Private Enterprise Numbers (PEN),

- 151 https://www.iana.org/assignments/enterprise-numbers

#### 152 3 Terms and definitions

- 153 In this document, some terms have a specific meaning beyond the normal English meaning. Those terms

- 154 are defined in this clause.

- The terms "shall" ("required"), "shall not", "should" ("recommended"), "should not" ("not recommended"),

- 156 "may", "need not" ("not required"), "can" and "cannot" in this document are to be interpreted as described

- in ISO/IEC Directives, Part 2, Clause 7. The terms in parentheses are alternatives for the preceding term,

- 158 for use in exceptional cases when the preceding term cannot be used for linguistic reasons. Note that

- 159 ISO/IEC Directives, Part 2, Clause 7 specifies additional alternatives. Occurrences of such additional

- alternatives shall be interpreted in their normal English meaning.

- The terms "clause", "subclause", "paragraph", and "annex" in this document are to be interpreted as

- described in ISO/IEC Directives, Part 2, Clause 6.

- The terms "normative" and "informative" in this document are to be interpreted as described in ISO/IEC

- 164 <u>Directives, Part 2</u>, Clause 3. In this document, clauses, subclauses, or annexes labeled "(informative)" do

- not contain normative content. Notes and examples are always informative elements.

- 166 Refer to Management Component Transport Protocol (MCTP) Base Specification for the terms and

- definitions that are used across the MCTP specifications.

- For the purposes of this document, the following terms and definitions apply.

- 169 **3.1**

- 170 **ACK**

- 171 Acknowledge

- 172 **3.2**

- 173 **B2H**

- 174 BMC-to-Host

- 175 **3.3**

- 176 **BAR**

- 177 Base Address Register

- 178 **3.4**

- 179 **(B)MC**

- 180 Baseboard Management Controller term used interchangeably with Management Controller

- 181 **3.5**

- 182 **CCT**

- 183 Control Command Type

- 184 **3.6**

- 185 **Destination Device**

- 186 Device receiving the MCTP packet over MMBI

- 187 **3.7**

- 188 **H2B**

- 189 Host-to-BMC

- 190 **3.8**

- 191 **MMBI**

- 192 Memory-Mapped Buffer Interface

- 193 **3.9**

- 194 **MMIO**

- 195 Memory-Mapped Input/Output

- 196 **3.10**

- 197 **NACK**

- 198 Not acknowledge

- 199 **3.11**

- 200 ROS

- 201 Read-Only Structure

- 202 **3.12**

- 203 **RWS**

- 204 Read-Write Structure

- 205 3.13

- 206 Source Device

- 207 Device sending the MCTP packet over MMBI

- 208 3.14

- 209 **SPDM**

- 210 Security Protocol and Data Model

- 211 **3.15**

- 212 **VPSCB**

- 213 Variable Packet Size Circular Buffer

#### 214 4 Conventions

The conventions described in the following clauses apply to this specification.

## 216 4.1 Reserved and unassigned values

- 217 Unless otherwise specified, any reserved, unspecified, or unassigned values in enumerations or other

- 218 numeric ranges are reserved for future definition by DMTF.

- 219 Unless otherwise specified, numeric or bit fields that are designated as reserved shall be written as 0

- 220 (zero) and ignored when read.

## 221 4.2 Byte ordering

- 222 Unless otherwise specified, byte ordering of multi-byte numeric fields or bit fields is "Big Endian" (that is,

- the lower byte offset holds the most significant byte, and higher offsets hold less-significant bytes).

# 224 5 Assumptions

225

231

236

### 5.1 Underlying Memory Mapping

- 226 The fundamental assumption in this specification is that there exists an underlying platform mechanism

- 227 allowing efficient memory sharing between the communicating entities (such as a host and a

- 228 management controller). PCIe MMIO is an example of such a mechanism. This specification defines the

- 229 packet transfer protocol on top of this assumed memory mapping layer.

- 230 Assumptions about the underlying layer are:

- 1) Memory mapping shall guarantee an error-free lossless channel.

- 232 2) The size of atomic operations is at least 4 bytes.

- The order of operations must be preserved: writes must be visible to the other party in the order they were executed by the sender; reads cannot be prefetched/cached; if interrupts are used,

- they must also obey the order of operations.

#### 5.2 Multiple Instances

- This specification has been designed with the assumption that a single MMBI instance will serve

- 238 communication between the two communicating entities only (typically host software and management

- 239 controller firmware components) and so the interface is not shared between multiple communicating

- 240 entities.

- Multiple components in the system, e.g., multiple host tenant / software agents communicating to a

- (B)MC, can be supported using a plurality of MMBI interfaces (each being an independent instance of the

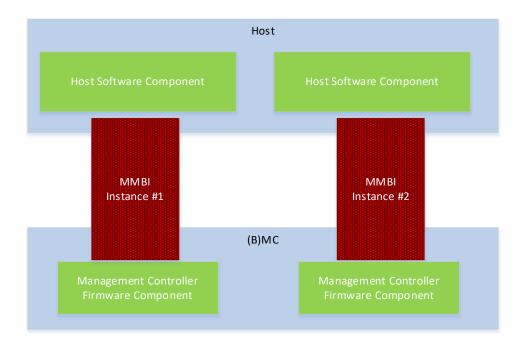

interface), located in different memory locations. Such MMBI instances shall operate independently as shown in Figure 1:

245

243

244

246

247

248

249

250

251

252

253

261

262263

264

265

Figure 1 - Multiple MMBI Instances

#### 5.3 Resets and Errors

MMBI allows lossless communication as well as graceful reset/initialization on request from a communicating party (in case of a reset of a software entity). However, MMBI does not provide guaranteed delivery in case of ungraceful resets of the communicating parties. Applications that care about data loss in such situations shall employ an ACK packet scheme to verify data reception by the other party and handle the error if ACK is not received.

## 5.4 Notifications (Interrupts)

- 254 MMBI is designed to execute in both interrupt and polling mode.

- The memory sharing capability may be accompanied by the ability to receive interrupts by the communicating software entities. MMBI enables discovery and enables use of the optional interrupt mechanism for efficient data exchange between communicating entities. If interrupts are used, it is assumed that the interrupt delivery mechanism is reliable.

- 259 If interrupts are not available, a polling mode can be used. Platform designers can choose polling or interrupt mode, based on their needs.

# 5.5 Packet Sizes, Types, and Packet Flow

MMBI allows variable packet sizes, with the maximum size dependent on the underlying physical layer's memory mapping capabilities. MMBI provides a discovery method allowing the communicating parties to define and discover the circular buffer sizes, which limit the maximum packet sizes that can be transmitted (fragmentation/reassembly is not supported by this version of MMBI protocol). The upper

- layers must adhere to the discovered limits and, if necessary, handle fragmentation/reassembly

- 267 accordingly.

- 268 MMBI allows multiple packets (datagrams) to be in-flight. That is, the sender can place more than one

- packet in the memory buffer even before they are consumed by the receiver. This enables asynchronous

- 270 operation of the communicating entities. Regardless of the number of packets in-flight, they are

- 271 guaranteed to arrive to the receiver in the FIFO order (note: upper layer can elect to process in same

- order or in different order, which will not be guaranteed by the MMBI layer). Note that if multiple instances

- of MMBI are in the system, they operate independently and no packet ordering guarantees exist between

- 274 them.

279

285

- 275 MMBI enables and defines discovery mechanisms to support the exchange of a variety of packet protocol

- 276 types, such as MCTP. Binding of these protocols to MMBI is defined in separate documents, such as

- 277 <u>Management Component Transport Protocol (MCTP) Memory-Mapped Buffer Interface (MMBI) Transport</u>

- 278 Binding Specification.

### 5.6 Security

- 280 MMBI does not provide any security guarantees. Any authentication, integrity protection, and/or

- 281 encryption is to be implemented by the other layers of the protocol stack. For example, for secure

- implementation of communication between the host and (B)MC using MMBI, <u>Secured Messages using</u>

- 283 <u>SPDM over MCTP Binding Specification</u> can be used. Another alternative can be host-based memory

- 284 protection mechanisms.

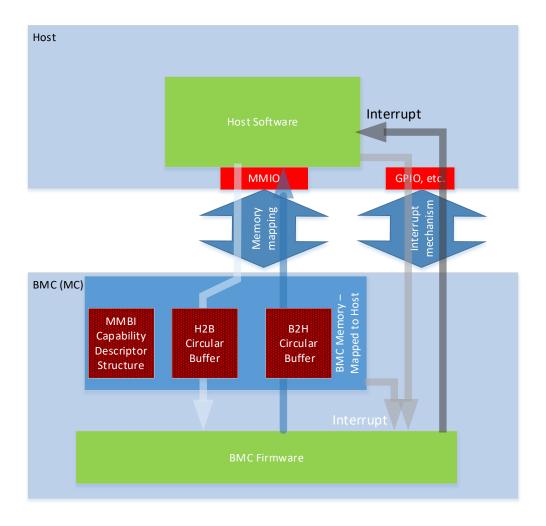

# 6 Basic Architecture Concept

- The host and the (B)MC use circular buffers to exchange data. One buffer is used to send data from the

- 287 host to the (B)MC and is referred to as H2B (Host-to-BMC). The other buffer is used for communication in

- the opposite direction and is referred to as B2H (BMC-to-Host). The buffers are used to store packet data.

- and they are accompanied by a descriptor structure. The descriptor is a data structure in the shared

- 290 memory used to store important capabilities and control information. These data structures are shown in

- Figure 2 and are defined in detail in section 7.

292

294

295

296

297 298

299 300

301

302 303

304

305 306

293 Figure 2 – MMBI Interface Concept Overview

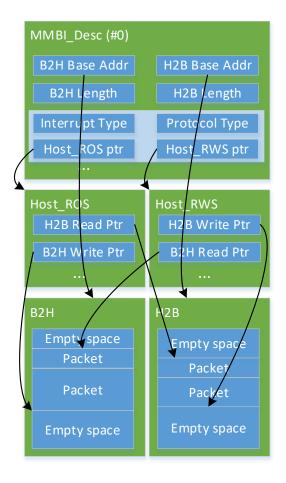

#### 7 MMBI Data Structures

Each instance of the MMBI interface is divided into sections as defined below:

- "BMC-to-Host" (B2H) region with substructure as follows:

- MMBI Capability Descriptor (MMBI\_Desc Structure) see section 7.1 for details

- Host\_ROS (Host Read-Only Structure) see section 7.2.3 for details

- o BMC-to-Host Circular buffer (B2H Circular buffer) see section 8 for details

- "Host-to-BMC" (H2B) region with substructure as follows:

- o Host\_RWS (Host Read-Write Structure) see section 7.2.2 for details

- o Host-to-BMC circular buffer (H2B Circular buffer) see section 8 for details

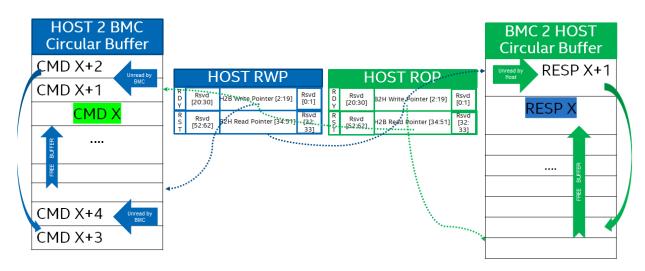

The format of the H2B and B2H circular buffers is a sequence of packets, and this format is referred to as Variable Packet Size Circular Buffer (VPSCB). For VPSCB, the relationships between these data structures and their main pointers are as presented in Figure 3.

Figure 3 – MMBI Data Structure Relationships

Details of these data structures are presented in the following subsections. Note that the data structures maintain 4-byte alignment for fields that need to be updated atomically. Packets in the circular buffers are also aligned to 4-byte boundaries.

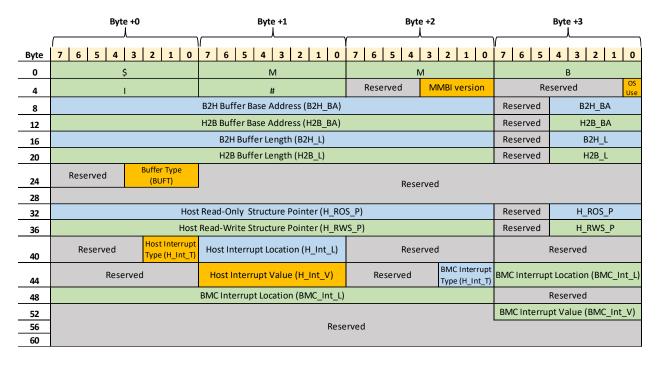

## 7.1 MMBI Capability Descriptor

MMBI Capability Descriptor is used to define the MMBI interface details. (B)MC updates this data structure during initialization. Other than that, the (B)MC and host are not allowed to update it. The host only reads this descriptor to understand the format of the MMBI data structures in memory and shall never write to this data structure. The layout of the structure is presented in Figure 4 and described in Table 1. See also section 8.1.

318

319

Figure 4 – MMBI Capability Descriptor Layout

## 320 Table 1 – MMBI Capability Descriptor Structure (MMBI\_Desc)

| · · · · · · · · · · · · · · · · · · · |                                                                                                                                 |  |  |  |  |  |  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Byte(s)                               | Description                                                                                                                     |  |  |  |  |  |  |

| 0:5                                   | MMBI Signature                                                                                                                  |  |  |  |  |  |  |

|                                       | "#MMBI\$" in ASCII. When this signature is not present, the host SW should assume the absence of MMBI.                          |  |  |  |  |  |  |

| 6                                     | [7:4] Reserved                                                                                                                  |  |  |  |  |  |  |

|                                       | [3:0] MMBI version                                                                                                              |  |  |  |  |  |  |

|                                       | 0001b - Implementations of MMBI described in this document shall indicate version 1 of MMBI.                                    |  |  |  |  |  |  |

| 7                                     | [7:1] Reserved                                                                                                                  |  |  |  |  |  |  |

|                                       | [0] OS Use                                                                                                                      |  |  |  |  |  |  |

|                                       | Indicates if this MMBI interface is intended for OS use:                                                                        |  |  |  |  |  |  |

|                                       | 0b – OS should not use this MMBI interface as it is managed by other host software components (UEFI BIOS, ACPI ASL code, etc.). |  |  |  |  |  |  |

|                                       | 1b - This MMBI interface is intended for OS use.                                                                                |  |  |  |  |  |  |

| 8:11                                  | [31:29] – Reserved                                                                                                              |  |  |  |  |  |  |

|                                       | [28:0] B2H Buffer Base Address (B2H_BA)                                                                                         |  |  |  |  |  |  |

|                                       | B2H (BMC-to-Host) buffer base address expressed in 8-byte units as offset relative to the beginning of the descriptor           |  |  |  |  |  |  |

| Byte(s) | Description                                                                                                                                       |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 12:15   | [31:29] – Reserved                                                                                                                                |  |  |  |  |  |  |

|         | [28:0] H2B Buffer Base Address (H2B_BA)                                                                                                           |  |  |  |  |  |  |

|         | H2B (Host-to-BMC) buffer base address expressed in 8-byte units as offset relative to the beginning of the descriptor                             |  |  |  |  |  |  |

| 16:19   | B2H Buffer Length (B2H_L)                                                                                                                         |  |  |  |  |  |  |

|         | The size of the B2H buffer (can represent up to 4GB)                                                                                              |  |  |  |  |  |  |

| 20:23   | H2B Buffer Length (H2B_L)                                                                                                                         |  |  |  |  |  |  |

|         | The size of the B2H buffer (can represent up to 4GB)                                                                                              |  |  |  |  |  |  |

|         |                                                                                                                                                   |  |  |  |  |  |  |

| 24      | [7:4] Reserved                                                                                                                                    |  |  |  |  |  |  |

|         | [3:0] Buffer Type (BUFT)                                                                                                                          |  |  |  |  |  |  |

|         | Indicates the type of data structures in H2B and B2H buffers. The following values are defined:                                                   |  |  |  |  |  |  |

|         | 0001b - MMBI Variable Packet Size Circular Buffers (VPSCB) v1 (see section 7.2)                                                                   |  |  |  |  |  |  |

|         | Other values are reserved.                                                                                                                        |  |  |  |  |  |  |

| 25:31   | Reserved                                                                                                                                          |  |  |  |  |  |  |

| 32:52   | Buffer Type Dependent Descriptor                                                                                                                  |  |  |  |  |  |  |

|         | The definition of this field is dependent on the BUFT field value:                                                                                |  |  |  |  |  |  |

|         | If BUFT=0001b (VPSCB), Table 2 in section 7.2 defines the format of these bytes and the packet format in circular buffers is defined in section 9 |  |  |  |  |  |  |

| 56:63   | Reserved                                                                                                                                          |  |  |  |  |  |  |

321

322

325

### 7.2 MMBI Circular Buffers—Variable Packet Size Circular Buffer

This section describes data structures used when the communication between (B)MC and host SW happens according to the VPSCB Buffer Type (BUFT=0001b).

## 7.2.1 Variable Packet Size Circular Buffer Descriptor

- Variable Packet Size Circular Buffer Descriptor is part of the *MMBI\_Desc* structure. Its access rules are the same as *MMBI\_Desc*:

- The (B)MC updates this data structure during MMBI interface initialization.

- Neither the (B)MC nor the host are allowed to update it at any other time.

# 330 Table 2 - Buffer Type Dependent Descriptor for BUFT=0001b (VPSCB Descriptor)

| Byte(s) | Description                                                                                                                                                |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0:3     | [31:29] – Reserved                                                                                                                                         |  |  |  |  |  |

|         | [28:0] Host Read-Only Structure Pointer (H_ROS_P)                                                                                                          |  |  |  |  |  |

|         | Points to the <i>Host_ROS</i> structure. The base address is expressed in 8-byte units as the offset relative to beginning of the descriptor               |  |  |  |  |  |

| 4:7     | [31:29] – Reserved                                                                                                                                         |  |  |  |  |  |

|         | [28:0] Host Read-Write Structure Pointer (H_RWS_P)                                                                                                         |  |  |  |  |  |

|         | Points to the <i>Host_RWS</i> structure. The base address is expressed in 8-byte units as the offset relative to beginning of the descriptor               |  |  |  |  |  |

| 8       | [7:3] – Reserved                                                                                                                                           |  |  |  |  |  |

|         | [2:0] Host Interrupt Type (H_Int_T)                                                                                                                        |  |  |  |  |  |

|         | Defines how the (B)MC interrupts the host. This is an informative field from the host's perspective with the intention to keep the (B)MC and host in sync. |  |  |  |  |  |

|         | 0 – no interrupt / polling                                                                                                                                 |  |  |  |  |  |

|         | 1 – PCIe interrupt (bus specific)                                                                                                                          |  |  |  |  |  |

|         | 2 – physical pin (GPIO)                                                                                                                                    |  |  |  |  |  |

|         | 3 – eSPI Virtual Wire                                                                                                                                      |  |  |  |  |  |

|         | Other values are reserved                                                                                                                                  |  |  |  |  |  |

| 9       | Host Interrupt Location (H_Int_L)                                                                                                                          |  |  |  |  |  |

|         | If H_Int_T = 0: reserved                                                                                                                                   |  |  |  |  |  |

|         | If H_Int_T = 1: for PCle, indicates the PCle interrupt message number                                                                                      |  |  |  |  |  |

|         | If H_Int_T = 2: pin number                                                                                                                                 |  |  |  |  |  |

|         | If H_Int_T = 3: eSPI Virtual Wire Index number                                                                                                             |  |  |  |  |  |

|         | Reserved otherwise                                                                                                                                         |  |  |  |  |  |

| 10:12   | Reserved                                                                                                                                                   |  |  |  |  |  |

| 13      | Host Interrupt Value (H_Int_V)                                                                                                                             |  |  |  |  |  |

|         | If H_Int_T = 3: eSPI Virtual Wire data value                                                                                                               |  |  |  |  |  |

|         | Reserved otherwise                                                                                                                                         |  |  |  |  |  |

| Byte(s) | Description                                                                                                             |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 14      | [7:3] – Reserved                                                                                                        |  |  |  |  |  |  |

|         |                                                                                                                         |  |  |  |  |  |  |

|         | [2:0] (B)MC Interrupt Type (BMC_Int_T)                                                                                  |  |  |  |  |  |  |

|         | Defines how the (B)MC wants to be interrupted:                                                                          |  |  |  |  |  |  |

|         | 0 - no interrupt triggering by the host                                                                                 |  |  |  |  |  |  |

|         | 1 – relative memory space address (offset defined in the BMC_Int_L field)                                               |  |  |  |  |  |  |

|         | 2 – Inband interrupt (bus specific—such as PCIe MSI or virtual legacy wire)                                             |  |  |  |  |  |  |

|         | Other values – reserved                                                                                                 |  |  |  |  |  |  |

| 15:18   | (B)MC Interrupt Location (BMC_Int_L)                                                                                    |  |  |  |  |  |  |

|         | If BMC_Int_T = 1, memory address—offset relative to the beginning of the <i>MMBI Capability Descriptor</i> base address |  |  |  |  |  |  |

|         | Otherwise reserved                                                                                                      |  |  |  |  |  |  |

| 19:22   | Reserved                                                                                                                |  |  |  |  |  |  |

| 23      | (B)MC Interrupt Value (BMC_Int_V)                                                                                       |  |  |  |  |  |  |

|         | If BMC_Int_T = 1, this field indicates the value to be written at the given address to trigger an interrupt.            |  |  |  |  |  |  |

|         | Otherwise reserved                                                                                                      |  |  |  |  |  |  |

#### 7.2.2 Host Read-Write Structure

331

332

333

334

335

336

337

338

The host's RW Structure Pointer in the above structure points to the *Host\_RWS* structure, which is shown in Table 1. This structure is accessed as follows:

- It is initialized by the (B)MC to the default values.

- The host updates this structure during normal communication—it is read-writeable for the host.

- The (B)MC is not allowed to write to this structure during normal communication—it should treat this structure as read-only (any kind of hardware-based enforcement of the read-only behavior is out of scope of this specification).

### Table 3 - MMBI Host Read-Write Structure (Host\_RWS)

| Byte(s) | Description                                                                                                                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:3     | [31:2] H2B Write Pointer (H2B_WP)                                                                                                                                                                                    |

|         | Bits [31:2] of the offset where the host can write the next data in the H2B circular buffer, counted from the beginning of the H2B buffer represented in 4-byte alignment.                                           |

|         | Bits [1:0] of the offset are assumed to always be zero (for 4-byte alignment).                                                                                                                                       |

|         | The (B)MC uses this pointer to determine how many bytes of valid data are present in the Circular Buffer (by comparing it with the H2B_RP offset).                                                                   |

|         | The host shall advance the pointer once data is written to the Circular Buffer and shall update this pointer to mark the next available offset.                                                                      |

|         | Note: The host shall not overwrite the data not read by the (B)MC, as indicated by the H2B_RP.                                                                                                                       |

|         | [1] Host Interface Up (H_UP)                                                                                                                                                                                         |

|         | 1 indicates that the host side of the interface is up and running, which means that the data structures can be used by the (B)MC.                                                                                    |

|         | [0] Host Reset Request (H_RST)                                                                                                                                                                                       |

|         | Setting this flag to 1 will initiate a reset sequence to get the circular buffers into a known good state (see section 8.1 for more information).                                                                    |

| 4:7     | [31:2] B2H Read Pointer (B2H_RP)                                                                                                                                                                                     |

|         | Bits [31:2] of the offset where the host reads data from the B2H circular buffer, counted from the beginning of the B2H buffer represented in 4-byte alignment.                                                      |

|         | Bits [1:0] of the offset are assumed to always be zero (for 4-byte alignment).                                                                                                                                       |

|         | The (B)MC uses this pointer to determine how much of data is read by the host. Comparing this with the B2H Write Pointer (B2H_WP) will provide how much space is left to write the data.                             |

|         | The host shall only advance the pointer once the data available in B2H is read by the host.                                                                                                                          |

|         | [1] Reserved                                                                                                                                                                                                         |

|         | [0] Host Ready (H_RDY)                                                                                                                                                                                               |

|         | 0 indicates that the host is performing some tasks that keep it busy, and so it may be unresponsive. However, the (B)MC can use the data structures and, for example, put data into the buffers as long as H_UP = 1. |

|         | 1 indicates that the host is ready to exchange data (see section 8.1 for more information).                                                                                                                          |

## 7.2.3 Host Read-Only Structure

340

339

Host RO Structure Pointer points to *Host\_ROS* structure. The host is only allowed to read this structure (never write). Any kind of hardware-based enforcement of the read-only behavior is out-of-scope of this specification. This structure is initialized by the (B)MC to the default values and later updated by (B)MC during normal communication—it is read-writeable for the (B)MC.

## Table 4 – MMBI Host Read-Only Structure (Host\_ROS)

345

346

347

348

349

| Byte(s) | Description                                                                                                                                                                                                    |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0:3     | [31:2] B2H Write Pointer (B2H_WP)                                                                                                                                                                              |  |  |  |  |

| 0.3     | Bits [31:2] of the offset where the (B)MC can write the next data in the B2H circular buffer, counted from the beginning of the B2H buffer.                                                                    |  |  |  |  |

|         | Bits [1:0] of the offset are assumed to always be zero (for 4-byte alignment).                                                                                                                                 |  |  |  |  |

|         | The host uses this pointer to determine how many bytes of valid data are present in the Circular Buffer (by comparing it with B2H_RP offset)                                                                   |  |  |  |  |

|         | The (B)MC shall advance the pointer once data is written to the Buffer to mark the next available offset.                                                                                                      |  |  |  |  |

|         | Note: (B)MC shall not overwrite the data not read by host, as indicated by the B2H_RP.                                                                                                                         |  |  |  |  |

|         | [1] (B)MC Interface Up (B_UP)                                                                                                                                                                                  |  |  |  |  |

|         | 1 indicates that the (B)MC side of the interface is up and running which means that the data structures are initialized and can be used                                                                        |  |  |  |  |

|         | [0] (B)MC Reset Request (B_RST)                                                                                                                                                                                |  |  |  |  |

|         | Setting this flag to 1 will initiate a reset sequence to get the circular buffers into a known good state (see section 8.1 for more information).                                                              |  |  |  |  |

| 4:7     | [31:2] H2B Read Pointer (H2B_RP)                                                                                                                                                                               |  |  |  |  |

| 7.1     | Bits [31:2] of the offset where the host reads data from the H2B circular buffer, counted from the beginning of the H2B buffer.                                                                                |  |  |  |  |

|         | Bits [1:0] of the offset are assumed to always be zero (for 4-byte alignment).                                                                                                                                 |  |  |  |  |

|         | The host uses this pointer to determine how much of data is read by the (B)MC. Comparing this with the H2B write pointer will provide how much space is left to write.                                         |  |  |  |  |

|         | (B)MC shall only advance the pointer once the data available in H2B is read by the (B)MC.                                                                                                                      |  |  |  |  |

|         | [1] Reserved                                                                                                                                                                                                   |  |  |  |  |

|         | [0] (B)MC Ready (B_RDY)                                                                                                                                                                                        |  |  |  |  |

|         | 0 indicates that the (B)MC is performing some tasks that keep it busy and so it may be unresponsive – host however can use the data structures and, for example, put data into the buffers as long as B_UP = 1 |  |  |  |  |

|         | 1 indicates that the (B)MC is ready to exchange data (see section 8.1 for more information).                                                                                                                   |  |  |  |  |

MMBI uses two circular buffers: H2B and B2H. Each buffer is a memory range defined in the descriptor with the following access:

- H2B (Host-to-BMC buffer) is RW for the host and RO for the (B)MC.

- B2H (BMC-to-Host buffer) is RO for the host and RW for the (B)MC.

- 350 The Read Pointer and Write Pointer are used to indicate the read and write location in the buffer. For

- as each read or write the pointer shall be advanced. It means pointer increment with a rollover at the buffer

- 352 size

357

358

379

- 353 These pointers, along with the Buffer Length fields (B2H\_L or H2B\_L), are used to calculate the number

- of filled bytes to read or the number of empty bytes available for write.

- 355 The circular buffers will be used to send packets of arbitrary size. A packet may require multiple memory

- 356 reads and/or write transfers.

## 8 Runtime Flows

#### 8.1 MMBI Interface Initialization and Reset

- This section describes the steps to allow the (B)MC to complete the initialization of the data structures

- and indicating when both sides of communication are ready to exchange data.

- The goal of the reset, on the other hand, is to reinitialize the data structures when at least one side wants

- a clean start, which may be due to unexpected device events, malfunction, error, etc. It may also be used

- 363 to reinitialize the data structures after, for example, a (B)MC firmware update in which the data structure

- 364 needs some new values (e.g., when the circular buffer size changes after the firmware update). A

- 365 graceful reset follows the state diagram presented in Figure 5, and it guarantees that MMBI protocol layer

- does not drop any packets (note that other protocol layers may still be unable to guarantee delivery).

- 367 The reset sequence is also automatically initiated when hardware errors lead to all-ones or all-zeros

- memory reads, as is typical with some media. This is thanks to the fact that when all the flags are zeros or

- are all ones, it indicates an initialization or transition to initialization states. Such unexpected resets do not

- follow the handshake protocol, and so are ungraceful and may lead to packet losses.

- 371 These flags are used to indicate the (B)MC's status as related to initialization and reset:

- (B)MC Interface Up (B UP)

- (B)MC Reset Request (B\_RST)

- 374 Similar flags are used to indicate the host's status:

- 4 Host Interface Up (H\_UP)

- Host Reset Request (H RST)

- All these flags are used in combination to achieve the proper handshake mechanism between the host

- and the (B)MC during initialization or reset.

#### 8.1.1 Initialization of Descriptor Structures after Power Up

- 380 The (B)MC must initialize the expected content of the MMBI data structures (see section 7) during power

- 381 up and make the shared memory available to the host. Initialization is expected to complete before the

- 382 host software accesses these structures so that the host can find the MMBI Capability Descriptor

- 383 (MMBI\_Desc) using the MMBI signature bytes. MMBI structures and buffers must always remain

- available in the shared memory when the host is using the MMBI interface.

- 385 During the initial accesses after the host's power up or reset, the host's software is expected to verify if

- 386 the content of the MMBI version and MMBI signature are as expected. If the above requirements are met,

- 387 the host is expected to check the interface state.

- 388 If the host's software does not find the proper MMBI Capability Descriptor (MMBI\_Desc) content at the

- 389 expected location, the host should consider the MMBI as not present or, optionally, it may implement a

- wait option with a timeout. Such a timeout mechanism is system-dependent and is out of scope of thisspecification.

- If the MMBI signature and MMBI version fields match, but the size and location of the buffers cannot be

- fulfilled by the host, it shall indicate the initialization mismatch error by transitioning to the *Initialization*

- 394 Mismatch state as described below. With this indication, the (B)MC may consider the interface as

- inoperable or attempt to reinitialize the *MMBI\_Desc* structure with, for example, a smaller buffer size.

- 396 Before updating the data structure content, the (B)MC shall first clear the B\_UP flag and then clear the

- 397 H\_RST flag to return back to the *Initialization in Progress* state. Such attempts to repair the situation are

- 398 system-dependent and are out of scope of this specification.

#### 8.1.2 Interface States and Graceful Reset

- 400 When \_RST and \_UP are both set on one side of communication, it means the entity is requesting a reset

- sequence. When B\_RST = H\_RST = B\_UP = H\_UP = 1, it means that both entities are ready to perform

- 402 the reset sequence (in fact, the host is just waiting for the (B)MC to do all the initialization).

- 403 All the states are summarized in Table 5. The "Host Write Access" and "(B)MC Write Access" columns

- define write-access restrictions to the data structures by host and (B)MC, respectively. There are no read

- 405 restrictions for the (B)MC and host. Note that the host is expected to re-read the data structure contents

- 406 after initialization is completed.

399

## Table 5 - MMBI Interface States

| B_UP | B_RST | H_UP | H_RST | State Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Host Write<br>Access                                                        | (B)MC Write<br>Access                                                     |

|------|-------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 0    | 0     | 0    | 0     | Initialization in Progress  The (B)MC is initializing the data structures.  The host can only monitor the data structures, waiting for B_UP = 1 and B_RST = 0 flags.                                                                                                                                                                                                                                                                                                   | Host not<br>allowed to<br>write to any<br>MMBI<br>structures                | (B)MC<br>allowed to<br>write to any<br>MMBI<br>structures                 |

| 1    | 0     | 0    | 0     | Initialization Completed  The (B)MC has completed initialization of the data structures and is ready to exchange data—waiting for the host to be ready. The host should re-read the MMBI_Desc structure and any dependent structures.  During this state, the (B)MC is allowed to deposit packets into the circular buffer.                                                                                                                                            | Host<br>allowed to<br>write to<br>MMBI<br>structures<br>as per<br>section 7 | (B)MC<br>allowed to<br>write to<br>MMBI<br>structures as<br>per section 7 |

| 1    | 0     | 1    | 0     | Normal Runtime  Both the (B)MC and host use the data structures and the circular buffers for data exchanges.                                                                                                                                                                                                                                                                                                                                                           | Host<br>allowed to<br>write to<br>MMBI<br>structures<br>as per<br>section 7 | (B)MC<br>allowed to<br>write to<br>MMBI<br>structures as<br>per section 7 |

| 1    | 1     | 1    | 0     | Reset Request by (B)MC  The (B)MC is requesting reset—waiting for the host to notice the request.  When the host notices the request, it should consume the data from the B2H (if any) and shall set H_RST flag as an ACK and wait for the initialization to complete (B_UP = 1 and B_RST = 0 status).                                                                                                                                                                 | Host<br>allowed to<br>write to<br>MMBI<br>structures<br>as per<br>section 7 | (B)MC<br>allowed to<br>write to<br>MMBI<br>structures as<br>per section 7 |

| 1    | 0     | 1    | 1     | Reset Request by Host  The host is requesting reset—waiting for the (B)MC to notice the request and reinitialize the interface. When the host sets the H_RST flag, it shall not perform any further updates in the MMBI data structures but shall only wait for the initialization to be completed by (B)MC (B_UP = 1 and B_RST = 0 status).  When the (B)MC notices the request, it should consume the data from the B2H (if any) and shall set B_RST flag as an ACK. | Host not<br>allowed to<br>write to any<br>MMBI<br>structures                | (B)MC<br>allowed to<br>write to any<br>MMBI<br>structures                 |

| B_UP | B_RST | H_UP | H_RST | State Description                                                                                                                                                                                                                                                                                                                                           | Host Write<br>Access                                         | (B)MC Write<br>Access                                     |

|------|-------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------|

| 1    | 1     | 1    | 1     | Reset ACKed  The host and (B)MC are ready to perform graceful interface reset. This is a transient state when the host is waiting for the (B)MC to complete the initialization. The host is not allowed to write to MMBI data structures. The (B)MC is expected to clear the B_UP and B_RST flags (in this order) and reinitialize all the data structures. | Host not<br>allowed to<br>write to any<br>MMBI<br>structures | (B)MC<br>allowed to<br>write to any<br>MMBI<br>structures |

| 0    | 1     | 1    | 1     | Transitioning to Initialization  Transient state after the "Reset ACKed" state. The host is not allowed to write to MMBI data structures.                                                                                                                                                                                                                   | Host not<br>allowed to<br>write to any<br>MMBI<br>structures | (B)MC<br>allowed to<br>write to any<br>MMBI<br>structures |

| 0    | 1     | 1    | 0     | Temporary Transition States                                                                                                                                                                                                                                                                                                                                 |                                                              |                                                           |

| 0    | 1     | 0    | 1     | These states may be observed during                                                                                                                                                                                                                                                                                                                         |                                                              |                                                           |

| 0    | 1     | 0    | 0     | initialization when the (B)MC updates the data structures (reinitialization of all the data structures is not an atomic operation).                                                                                                                                                                                                                         | Host not allowed to write to any                             | (B)MC<br>allowed to<br>write to any                       |

| 0    | 0     | 0    | 1     | They are unexpected during normal operation and if they happen it means that MMBI structures have been corrupted. The (B)MC may initialize the interface or stop using MMBI and report a fatal error.                                                                                                                                                       | MMBI<br>structures                                           | MMBI<br>structures                                        |

| 1    | 0     | 0    | 1     | Initialization Mismatch The host causes transition into this state from Initialization Completed when it is unable to use the interface due to unsupported content in the MMBI Capability Descriptor structure.                                                                                                                                             |                                                              |                                                           |

| 1    | 1     | 0    | 1     | Unexpected States                                                                                                                                                                                                                                                                                                                                           |                                                              |                                                           |

| 1    | 1     | 0    | 0     | These states shall never happen:  • If the (B)MC reads this state, it                                                                                                                                                                                                                                                                                       | Host not allowed to write to any                             | (B)MC<br>allowed to<br>write to any                       |

| 0    | 0     | 1    | 0     | indicates that the host does not follow MMBI MMBI protocol or some other                                                                                                                                                                                                                                                                                    |                                                              | MMBI<br>structures                                        |

| 0    | 0     | 1    | 1     | corruption happened—the (B)MC should initialize the interface or it may stop using MMBI and report a fatal error, depending on system policy.  If the host reads this state, it may wait for the reinitialization to complete or stop using MMBI and report a fatal error, depending on system policy.                                                      | 5 45.41.55                                                   | 335                                                       |

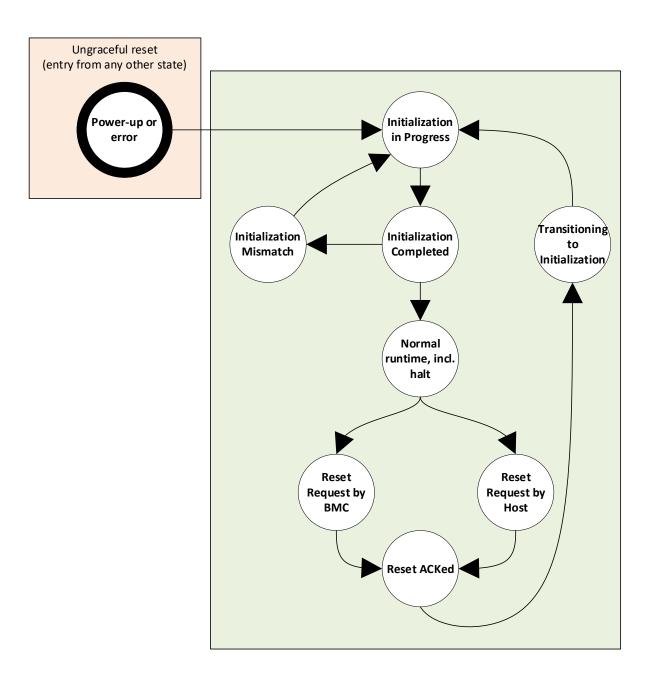

The expected state transitions are presented in Figure 5:

409

408

410

411

Figure 5 - MMBI Interface States

412

413

414

The host shall check the MMBI Interface state before writing any new data to the H2B buffer (as

described in Table 5, the host is only allowed to transfer new data in the Normal Runtime state, i.e.,

B\_UP=1 & B\_RST=0 & H\_UP=1 & H\_RST=0). Similarly, the (B)MC shall check the status before writing

any new data to the B2H buffer. These status flags are conveniently located in the B2H\_WP or H2B\_WP bytes which the host or (B)MC, respectively, read anyway during any use of the circular buffers.

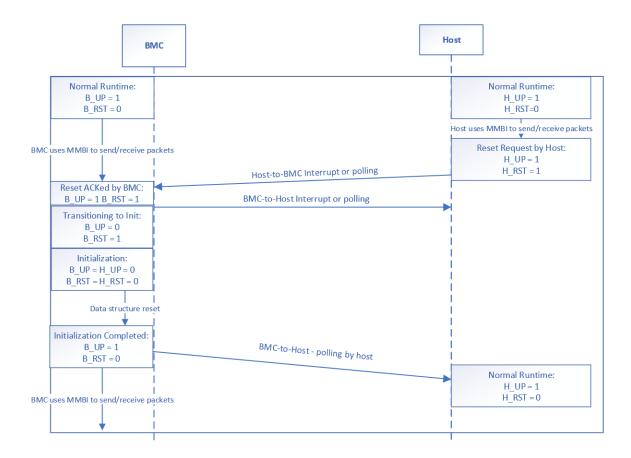

#### 8.1.2.1 Host Initiating Graceful Reset Sequence

Assuming *Normal Runtime* state, the host shall use the following sequence to request MMBI interface reset:

- 1) The host sets H\_RST = 1 to initiate the reset flow. If (B)MC interrupts are enabled, the host notifies the (B)MC.

- a. In response, the (B)MC is expected to set B\_RST = 1, which indicates the transition to the *Reset ACKed* state. If host interrupts are enabled, the host is expected to be notified about the update (or else it uses polling). At this point, the (B)MC reinitializes all the data structures.

- 2) The host waits for B\_UP = 1 and B\_RST = 0 (and H\_UP = H\_RST = 0), which indicates the transition to the *Initialization Completed* state. Host interrupts are not used at this stage until H\_UP is set by host software.

- 3) The host transitions to the *Normal Runtime* state by setting H\_UP = 1. The host is also expected to set the B\_RDY flag, indicating that it can receive and handle new packets—see section 8.3. If (B)MC interrupts are enabled, the host notifies the (B)MC after the flags are updated.

- 432 Figure 6 presents a sample flow:

Figure 6 - Sample MMBI Reset by Host

26 Published Version 1.0.1

| 435 | 8.1.2.2 | (B)MC Initiating Graceful Reset Sequence | е |

|-----|---------|------------------------------------------|---|

|-----|---------|------------------------------------------|---|

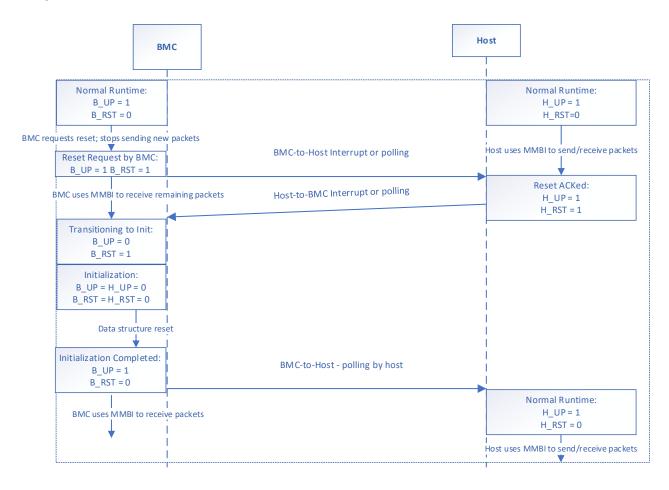

Assuming *Normal Runtime* state, the (B)MC shall use the following sequence to request MMBI interface reset:

- 438 1) The (B)MC sets B\_RST = 1 to initiate the reset flow. If host interrupts are enabled, the (B)MC 439 notifies the host.

- The (B)MC waits for H\_UP = 1 and H\_RST = 1, which indicates the transition to the *Reset ACKed* state. If (B)MC interrupts are enabled, the (B)MC is expected to be notified about the update (or else (B)MC uses polling).

- 3) The (B)MC clears the B\_UP flag (B\_RST still set). Host interrupts are no longer enabled.

- 4) The (B)MC clears the H\_UP and H\_RST flags (this may cause transient states to be observed by the host).

- 446 5) The (B)MC clears the B RST flag.

- 447 6) The (B)MC reinitializes all the data structures.

- The (B)MC sets B\_UP = 1. Host interrupts are not used at this stage until H\_UP is set by host software.

- 450 8) The (B)MC waits for the host to set H\_UP = 1. If (B)MC interrupts are enabled, the (B)MC is expected to be notified about the update.

- Note that the (B)MC is also expected to set the B\_RDY flag, typically in step 7, indicating that it can receive and handle new packets—see section 8.3.

- 454 Figure 7 presents a sample flow.

Figure 7 - Sample MMBI Reset by (B)MC

#### 8.1.3 Ungraceful Reset Considerations

If an ungraceful reset/crash happens, MMBI does not guarantee delivery. However, provisions are present in the MMBI design to handle the following scenarios:

- 1. In the case of a (B)MC FW-only reset (HW continues to work, memory content, including buffers stay intact in shared memory and accesses are still handled by HW): the host will still see the MMBI in the normal state and write to MMBI Circular buffers to deposit or read data as long as there is any space available in the buffers. In this situation, host may timeout waiting for a response but this is handled by higher layers above MMBI.

- 2. (B)MC HW reset (buffers are wiped and MMIO mechanisms are broken): the host will see errors on reads/writes and must handle them as per host-specific mechanisms. Additionally, MMBI encoding of status in B\_UP, B\_RST, H\_UP, & H\_RST is such that all-zeros or all-ones are recognized as transient states (see Table 5). So, even if there would be no other mechanisms in the system, the host would still recognize this as an error and would have to wait for reinitialization by the (B)MC (the host is not allowed to write to the buffers in the transient state, i.e., until the data structures are reinitialized by (B)MC FW).

- 3. Unexpected host reset (SW or HW reset is the same outcome): the host's unexpected reset will leave the data structures intact in (B)MC memory, so the (B)MC can still read the data from the buffers. Assuming the (B)MC understands the host's status via other mechanisms, the (B)MC can take informed decisions about how to respond to such situations.

476 In all the above cases, MMBI data structures can be reinitialized after the reset to allow a clean restart.

### 8.2 Calculation of Filled Space and Empty Space in Circular Buffer

The procedure for calculating the number of filled bytes in a circular buffer is analogous for both the H2B and B2H buffers: the difference between the write pointer and read pointer indicates the amount of valid data, accounting for the rollover at the end of the buffer. The write pointer cannot advance beyond the read pointer, accounting for the rollover at the end of the buffer.

The following steps allow calculation of the number of filled slots in a circular buffer:

- 1. The write and read pointers must start with zero after initialization. Since read pointer = write pointer, there is no valid data/packets in the buffer on initialization.

- 2. Once data is written to the buffer, the source (the host or (B)MC) will advance the write buffer pointer.

- 3. Read pointer is advanced once data is read/consumed by the receiver (the host or (B)MC).

- 4. Rollover: when the pointers reach the maximum offset within the buffer during writing/reading, data must be written/read starting back at zero offset, and the pointers roll over accordingly.

Figure 8 - Filled and Empty Space in Circular Buffers

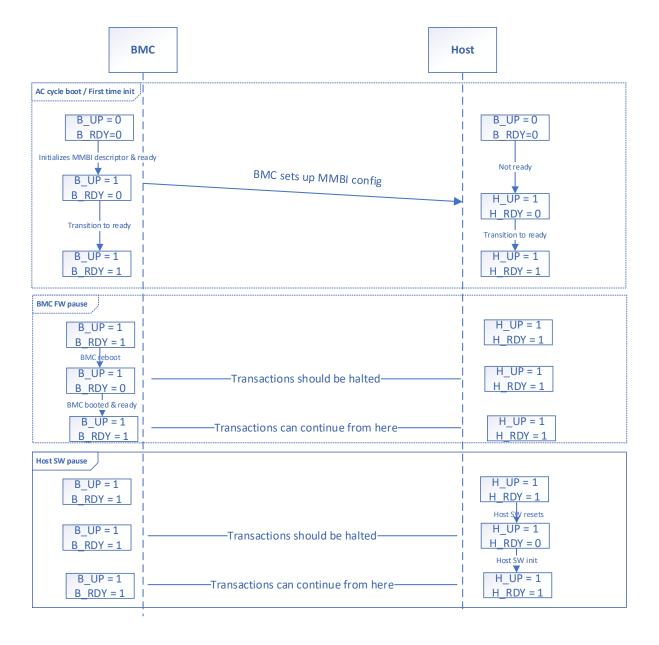

#### 8.3 Device Readiness and Communication Pause

In addition to the reinitialization or reset states, the MMBI interface also uses the H\_RDY and B\_RDY flags to indicate the device's readiness to consume incoming packets and handle them. When the host or (B)MC are ready to receive and handle packets, they set the B\_RDY or H\_RDY flags, respectively. If a B\_RDY or H\_RDY flag is clear but the B\_UP and H\_UP flags are set, it means that the MMBI interface is up but the target device is not ready to consume and handle new packets. When the interface is up, it means that the data structures are ready to accept new packets so the sender can: